# 1.1nV/√Hz Noise, Low Power, Precision Operational Amplifier in Small DFN-8 Package

#### **FEATURES**

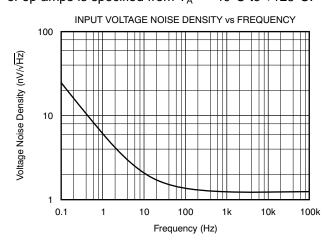

- LOW VOLTAGE NOISE: 1.1nV/√Hz at 1kHz

- INPUT VOLTAGE NOISE: 80nV<sub>PP</sub> (0.1Hz to 10Hz)

- THD+N: -136dB (G = 1, f = 1kHz)

- OFFSET VOLTAGE: 125μV (max)

- OFFSET VOLTAGE DRIFT: 0.35μV/°C (typ)

- LOW SUPPLY CURRENT: 3.6mA/Ch (typ)

- UNITY-GAIN STABLE

- GAIN BANDWIDTH PRODUCT: 80MHz (G = 100) 45MHz (G = 1)

- SLEW RATE: 27V/μs

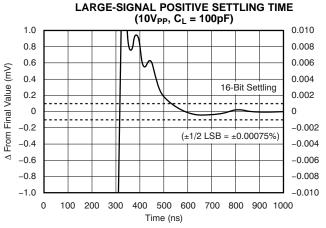

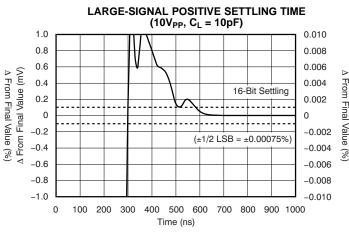

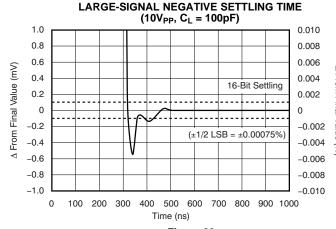

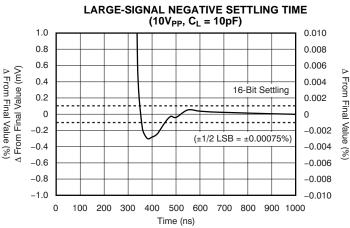

- 16-BIT SETTLING: 700ns

- WIDE SUPPLY RANGE: ±2.25V to ±18V, +4.5V to +36V

- RAIL-TO-RAIL OUTPUT

- OUTPUT CURRENT: 30mA

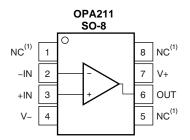

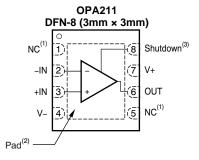

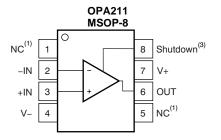

- DFN-8 (3mm × 3mm), MSOP-8, AND SO-8

#### **APPLICATIONS**

- PLL LOOP FILTER

- LOW-NOISE, LOW-POWER SIGNAL PROCESSING

- 16-BIT ADC DRIVERS

- DAC OUTPUT AMPLIFIERS

- ACTIVE FILTERS

- LOW-NOISE INSTRUMENTATION AMPS

- ULTRASOUND AMPLIFIERS

- PROFESSIONAL AUDIO PREAMPLIFIERS

- LOW-NOISE FREQUENCY SYNTHESIZERS

- INFRARED DETECTOR AMPLIFIERS

- HYDROPHONE AMPLIFIERS

- GEOPHONE AMPLIFIERS

- MEDICAL

#### DESCRIPTION

The OPA211 series of precision operational amplifiers achieves very low 1.1nV/\(\sqrt{Hz}\) noise density with a supply current of only 3.6mA. This series also offers rail-to-rail output swing, which maximizes dynamic range.

The extremely low voltage and low current noise, high speed, and wide output swing of the OPA211 series make these devices an excellent choice as a loop filter amplifier in PLL applications.

In precision data acquisition applications, the OPA211 series of op amps provides 700ns settling time to 16-bit accuracy throughout 10V output swings. This ac performance, combined with only  $125\mu V$  of offset and  $0.35\mu V/^{\circ}C$  of drift over temperature, makes the OPA211 ideal for driving high-precision 16-bit analog-to-digital converters (ADCs) or buffering the output of high-resolution digital-to-analog converters (DACs).

The OPA211 series is specified over a wide dual-power supply range of ±2.25V to ±18V, or for single-supply operation from +4.5V to +36V.

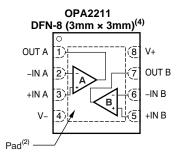

The OPA211 is available in the small DFN-8 (3mm  $\times$  3mm), MSOP-8, and SO-8 packages. A dual version, the OPA2211, is available in the DFN-8 (3mm  $\times$  3mm) or an SO-8 PowerPAD<sup>TM</sup> package. This series of op amps is specified from  $T_A = -40^{\circ}\text{C}$  to +125°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ABSOLUTE MAXIMUM RATINGS(1)

Over operating free-air temperature range (unless otherwise noted).

|                                     |                               |                     | VALUE                    | UNIT |  |  |

|-------------------------------------|-------------------------------|---------------------|--------------------------|------|--|--|

| Supply Voltage                      |                               | $V_S = (V+) - (V-)$ | 40                       | V    |  |  |

| Input Voltage                       |                               |                     | (V–) – 0.5 to (V+) + 0.5 | V    |  |  |

| Input Current (Any                  | pin except power-supply pins) |                     | ±10                      | mA   |  |  |

| Output Short-Circuit <sup>(2)</sup> |                               |                     | Continuous               |      |  |  |

| Operating Temper                    | ature                         | (T <sub>A</sub> )   | −55 to +150              | °C   |  |  |

| Storage Temperat                    | ure                           | (T <sub>A</sub> )   | -65 to +150              | °C   |  |  |

| Junction Temperature                |                               | (T <sub>J</sub> )   | 200                      | °C   |  |  |

| ESD Botings                         | Human Body Model (HBM)        |                     | 3000                     | V    |  |  |

| ESD Ratings                         | Charged Device Model (CDM)    |                     | 1000                     | V    |  |  |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

(2) Short-circuit to V<sub>S</sub>/2 (ground in symmetrical dual supply setups), one amplifier per package.

#### PACKAGE/ORDERING INFORMATION(1)

| PRODUCT        | PACKAGE-LEAD                     | SINGLE | SHUTDOWN | DUAL | PACKAGE<br>DESIGNATOR | PACKAGE<br>MARKING |

|----------------|----------------------------------|--------|----------|------|-----------------------|--------------------|

| Standard Grade |                                  |        |          |      |                       |                    |

|                | DFN-8 (3mm × 3mm)                | ✓      | ✓        |      | DRG                   | OBDQ               |

| OPA211AI       | MSOP-8                           | ✓      | ✓        |      | DGK                   | OBCQ               |

| OFAZITAI       | SO-8                             | ✓      |          |      | D                     | A TI OPA<br>211    |

|                | DFN-8 (3mm × 3mm) <sup>(2)</sup> |        |          | ✓    | DRG                   | OBHQ               |

| OPA2211AI      | SO-8 PowerPAD <sup>(2)</sup>     |        |          | ✓    | DDA                   | A TI OPA<br>2211   |

| High Grade     |                                  |        |          |      |                       |                    |

|                | DFN-8 (3mm × 3mm)                | ✓      | ✓        |      | DRG                   | OBDQ               |

| OPA211I        | MSOP-8                           | ✓      | ✓        |      | DGK                   | OBCQ               |

|                | SO-8                             | ✓      |          |      | D                     | TI OPA<br>211      |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

Product preview devices.

#### **PIN CONFIGURATIONS**

- (1) NC denotes no internal connection. Pin can be left floating or connected to any voltage between (V-) and (V+).

- (2) Exposed thermal die pad on underside; connect thermal die pad to V-. Soldering the thermal pad improves heat dissipation and provides specified performance.

- (3) Shutdown function:

- Device enabled: (V−) ≤ V<sub>SHUTDOWN</sub> ≤ (V+) − 3V

- Device disabled: V<sub>SHUTDOWN</sub> ≥ (V+) 0.35V

- (4) Product preview device.

#### ELECTRICAL CHARACTERISTICS: $V_s = \pm 2.25V$ to $\pm 18V$

**BOLDFACE** limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to +125°C. At  $T_A = +25^{\circ}C$ ,  $R_L = 10k\Omega$  connected to midsupply,  $V_{CM} = V_{OUT} =$  midsupply, unless otherwise noted.

| PARAMETER                                                                                                         |                      |                                                                |            | andard Grad<br>11AI, OPA22 |            |            |                      |            |                       |

|-------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------|------------|----------------------------|------------|------------|----------------------|------------|-----------------------|

|                                                                                                                   |                      | CONDITIONS                                                     | MIN        | TYP                        | MAX        | MIN        | TYP                  | MAX        | UNIT                  |

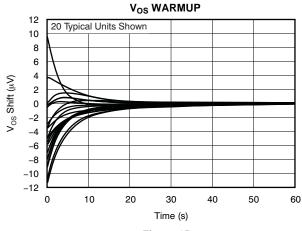

| OFFSET VOLTAGE                                                                                                    |                      |                                                                |            |                            |            |            |                      |            |                       |

| Input Offset Voltage                                                                                              | $V_{OS}$             | V <sub>S</sub> = ±15V                                          |            | ±30                        | ±125       |            | ±20                  | ±50        | μV                    |

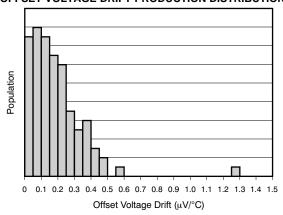

| Drift                                                                                                             | dV <sub>os</sub> /dT |                                                                |            | 0.35                       | 1.5        |            | 0.15                 | 0.85       | μ <b>۷/°C</b>         |

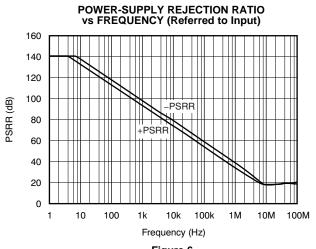

| vs Power Supply                                                                                                   | PSRR                 | $V_S = \pm 2.25 V \text{ to } \pm 18 V$                        |            | 0.1                        | 1          |            | 0.1                  | 0.5        | μV/V                  |

| Over Temperature                                                                                                  |                      |                                                                |            |                            | 3          |            |                      | 3          | μ <b>V/V</b>          |

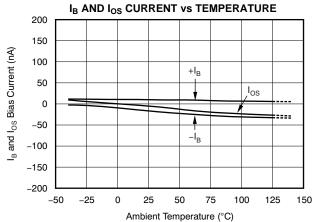

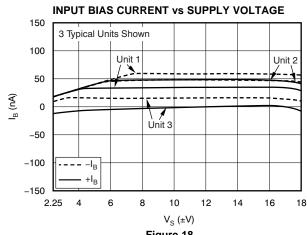

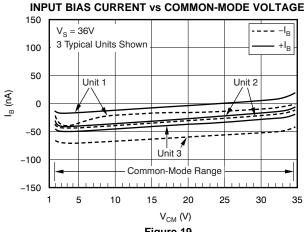

| INPUT BIAS CURRENT                                                                                                |                      |                                                                |            |                            |            |            |                      |            |                       |

| Input Bias Current                                                                                                | $I_{B}$              | V <sub>CM</sub> = 0V                                           |            | ±60                        | ±175       |            | ±50                  | ±125       | nA                    |

| Over Temperature                                                                                                  |                      |                                                                |            |                            | ±200       |            |                      | ±200       | nA                    |

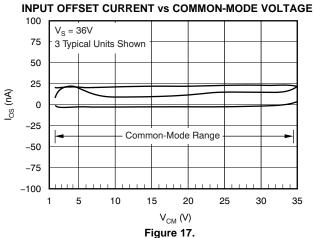

| Offset Current                                                                                                    | Ios                  | V <sub>CM</sub> = 0V                                           |            | ±25                        | ±100       |            | ±20                  | ±75        | nA                    |

| Over Temperature                                                                                                  |                      |                                                                |            |                            | ±150       |            |                      | ±150       | nA                    |

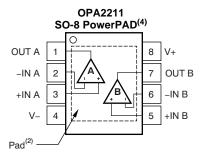

| NOISE                                                                                                             |                      |                                                                |            |                            |            |            |                      |            |                       |

| Input Voltage Noise                                                                                               | $\boldsymbol{e}_{n}$ | f = 0.1Hz to 10Hz                                              |            | 80                         |            |            | 80                   |            | $nV_{PP}$             |

| Input Voltage Noise Density                                                                                       |                      | f = 10Hz                                                       |            | 2                          |            |            | 2                    |            | nV/√ <del>Hz</del>    |

|                                                                                                                   |                      | f = 100Hz                                                      |            | 1.4                        |            |            | 1.4                  |            | nV/√ <del>Hz</del>    |

|                                                                                                                   |                      | f = 1kHz                                                       |            | 1.1                        |            |            | 1.1                  |            | nV/√ <del>Hz</del>    |

| Input Current Noise Density                                                                                       | $I_n$                | f = 10Hz                                                       |            | 3.2                        |            |            | 3.2                  |            | pA/√ <del>Hz</del>    |

|                                                                                                                   |                      | f = 1kHz                                                       |            | 1.7                        |            |            | 1.7                  |            | pA/√ <del>Hz</del>    |

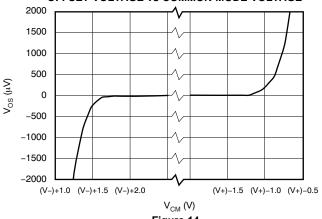

| INPUT VOLTAGE RANGE                                                                                               |                      |                                                                |            |                            |            |            |                      |            |                       |

| Common-Mode Voltage Range                                                                                         | $V_{CM}$             | V <sub>S</sub> ≥ ±5V                                           | (V-) + 1.8 |                            | (V+) - 1.4 | (V-) + 1.8 |                      | (V+) - 1.4 | V                     |

|                                                                                                                   |                      | $V_S < \pm 5V$                                                 | (V-) + 2   |                            | (V+) - 1.4 | (V-) + 2   |                      | (V+) - 1.4 | V                     |

| Common-Mode Rejection Ratio                                                                                       | CMRR                 | $V_S \ge \pm 5V$ , $(V-) + 2V \le V_{CM} \le (V+) - 2V$        | 114        | 120                        |            | 114        | 120                  |            | dB                    |

|                                                                                                                   |                      | $V_S < \pm 5V, (V-) + 2V \le V_{CM} \le (V+) - 2V$             | 110        | 120                        |            | 110        | 120                  |            | dB                    |

| INPUT IMPEDANCE                                                                                                   |                      |                                                                |            |                            |            |            |                      |            |                       |

| Differential                                                                                                      |                      |                                                                |            | 20k    8                   |            |            | 20k    8             |            | $\Omega \parallel pF$ |

| Common-Mode                                                                                                       |                      |                                                                |            | 10 <sup>9</sup>    2       |            |            | 10 <sup>9</sup>    2 |            | Ω    pF               |

| OPEN-LOOP GAIN                                                                                                    |                      |                                                                |            |                            |            |            |                      |            |                       |

| Open-Loop Voltage Gain                                                                                            | $\mathbf{A}_{OL}$    | $(V-) + 0.2V \le V_0 \le (V+) - 0.2V,$<br>$R_L = 10k\Omega$    | 114        | 130                        |            | 114        | 130                  |            | dB                    |

|                                                                                                                   | $A_OL$               | $(V-) + 0.6V \le V_0 \le (V+) - 0.6V,$<br>$R_L = 600\Omega$    | 110        | 114                        |            | 110        | 114                  |            | dB                    |

| Over Temperature                                                                                                  | A <sub>OL</sub>      | $(V-) + 0.6V \le V_0 \le (V+) - 0.6V,$<br>$I_0 \le 15mA$       | 110        |                            |            | 110        |                      |            | dB                    |

|                                                                                                                   | A <sub>OL</sub>      | $(V-) + 0.6V \le V_0 \le (V+)-0.6V,$<br>15mA < $I_0 \le 30$ mA | 103        |                            |            | 103        |                      |            | dB                    |

| FREQUENCY RESPONSE                                                                                                |                      |                                                                |            |                            |            |            |                      |            |                       |

| Gain-Bandwidth Product                                                                                            | GBW                  | G = 100                                                        |            | 80                         |            |            | 80                   |            | MHz                   |

|                                                                                                                   |                      | G = 1                                                          |            | 45                         |            |            | 45                   |            | MHz                   |

| Slew Rate                                                                                                         | SR                   |                                                                |            | 27                         |            |            | 27                   |            | V/μs                  |

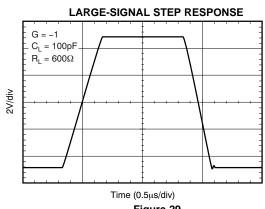

| Settling Time, 0.01%                                                                                              | $t_S$                | $V_S = \pm 15V, G = -1, 10V \text{ Step}, C_L = 100pF$         |            | 400                        |            |            | 400                  |            | ns                    |

| 0.0015% (16-bit)                                                                                                  |                      | $V_S = \pm 15V, G = -1, 10V \text{ Step}, C_L = 100pF$         |            | 700                        |            |            | 700                  |            | ns                    |

| Overload Recovery Time                                                                                            |                      | G = -10                                                        |            | 500                        |            |            | 500                  |            | ns                    |

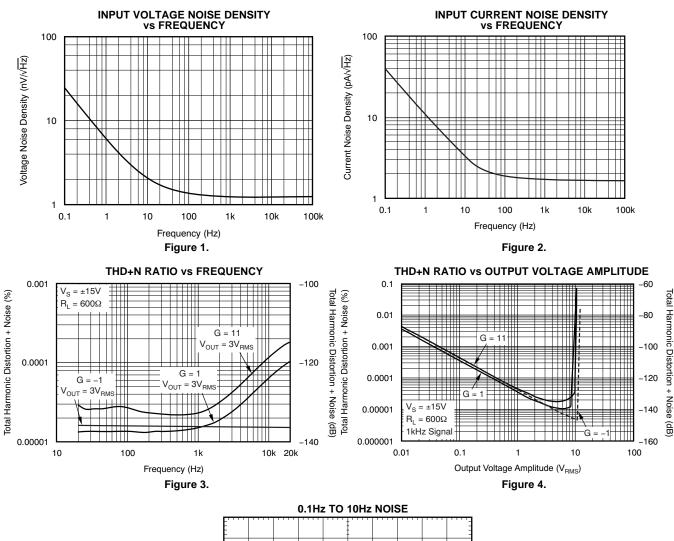

| Total Harmonic Distortion + Noise THD+N $G = +1, f = 1 \text{kHz}, \\ V_O = 3 V_{\text{RMS}}, \ R_L = 600 \Omega$ |                      |                                                                |            | 0.000015                   |            |            | 0.000015             |            | %                     |

|                                                                                                                   |                      |                                                                |            | -136                       |            |            | -136                 |            | dB                    |

<sup>(1)</sup> Shaded cells indicate different specifications from standard-grade version of device.

### ELECTRICAL CHARACTERISTICS: $V_S = \pm 2.25V$ to $\pm 18V$ (continued)

**BOLDFACE** limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to +125°C. At  $T_A = +25^{\circ}C$ ,  $R_L = 10k\Omega$  connected to midsupply,  $V_{CM} = V_{OUT} =$  midsupply, unless otherwise noted.

| PARAMETER                       |                    |                                                |             | andard Grad<br>11AI, OPA22 |            |             |               |            |      |

|---------------------------------|--------------------|------------------------------------------------|-------------|----------------------------|------------|-------------|---------------|------------|------|

|                                 |                    | CONDITIONS                                     | MIN         | MIN TYP MAX                |            | MIN         | TYP           | MAX        | UNIT |

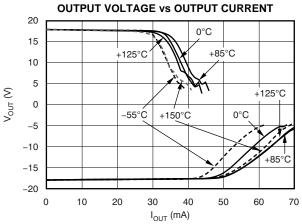

| OUTPUT                          |                    |                                                |             |                            |            |             |               |            |      |

| Voltage Output                  | $\mathbf{v}_{out}$ | $R_L = 10k\Omega$ , $A_{OL} \ge 114dB$         | (V-) + 0.2  |                            | (V+) - 0.2 | (V-) + 0.2  |               | (V+) - 0.2 | ٧    |

|                                 |                    | $R_L = 600\Omega$ , $A_{OL} \ge 110dB$         | (V-) + 0.6  |                            | (V+) - 0.6 | (V-) + 0.6  |               | (V+) - 0.6 | V    |

|                                 |                    | I <sub>O</sub> < 15mA, A <sub>OL</sub> ≥ 110dB | (V-) + 0.6  |                            | (V+) - 0.6 | (V-) + 0.6  |               | (V+) - 0.6 | ٧    |

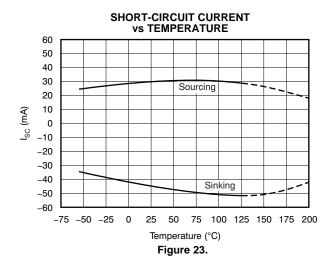

| Short-Circuit Current           | I <sub>sc</sub>    |                                                |             | +30/-45                    |            |             | +30/–45       |            | mA   |

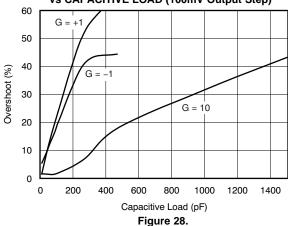

| Capacitive Load Drive           | C <sub>LOAD</sub>  |                                                | See Typ     | ical Charact               | eristics   | See Typ     | oical Charact | eristics   | pF   |

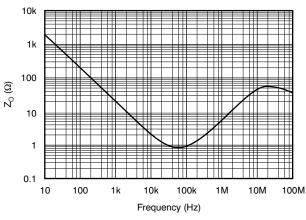

| Open-Loop Output Impedance      | Zo                 | f = 1MHz                                       |             | 5                          |            |             | 5             |            | Ω    |

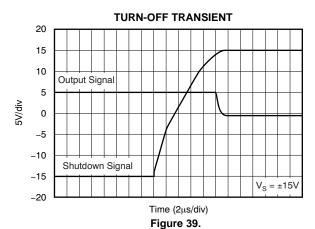

| SHUTDOWN                        |                    |                                                |             |                            |            |             |               |            |      |

| Shutdown Pin Input Voltage (2)  |                    | Device disabled (shutdown)                     | (V+) - 0.35 |                            |            | (V+) - 0.35 |               |            | V    |

|                                 |                    | Device enabled                                 |             |                            | (V+) - 3   |             |               | (V+) - 3   | V    |

| Shutdown Pin Leakage Current    |                    |                                                |             | 1                          |            |             | 1             |            | μΑ   |

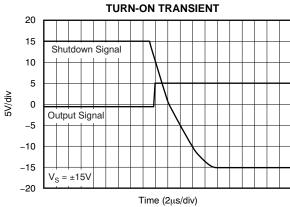

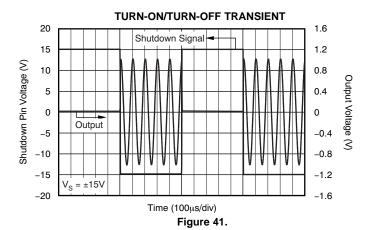

| Turn-On Time <sup>(3)</sup>     |                    |                                                |             | 2                          |            |             | 2             |            | μs   |

| Turn-Off Time <sup>(3)</sup>    |                    |                                                |             | 3                          |            |             | 3             |            | μs   |

| Shutdown Current                |                    | Shutdown (disabled)                            |             | 1                          | 20         |             | 1             | 20         | μΑ   |

| POWER SUPPLY                    |                    |                                                |             |                            |            |             |               |            |      |

| Specified Voltage               | Vs                 |                                                | ±2.25       |                            | ±18        | ±2.25       |               | ±18        | V    |

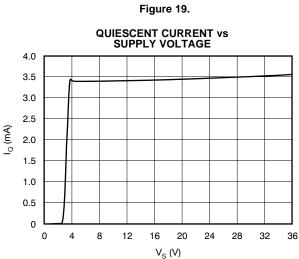

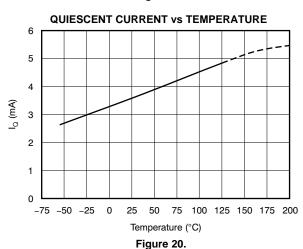

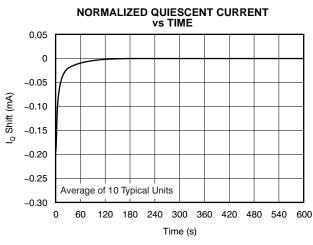

| Quiescent Current (per channel) | ΙQ                 | $I_{OUT} = 0A$                                 |             | 3.6                        | 4.5        |             | 3.6           | 4.5        | mA   |

| Over Temperature                |                    |                                                |             |                            | 6          |             |               | 6          | mA   |

| TEMPERATURE RANGE               |                    |                                                |             |                            |            |             |               |            |      |

| Specified Range                 |                    | T <sub>A</sub>                                 | -40         |                            | +125       | -40         |               | +125       | °C   |

| Operating Range                 |                    | T <sub>A</sub>                                 | -55         |                            | +150       | -55         |               | +150       | °C   |

| Thermal Resistance              |                    |                                                |             |                            |            |             |               |            |      |

| DFN (3mm × 3mm)                 | $\theta$ JA        | High-K board                                   |             | 65                         |            |             | 65            |            | °C/W |

|                                 | θ <sub>JC</sub>    |                                                |             | 57                         |            |             | 57            |            | °C/W |

| MSOP-8                          | $\theta$ JA        |                                                |             | 200                        |            |             | 200           |            | °C/W |

| SO-8                            | θ <sub>JA</sub>    |                                                |             | 150                        |            |             | 150           |            | °C/W |

| SO-8 PowerPAD                   | θ <sub>JA</sub>    | High-K board                                   |             | 52                         |            |             | 52            |            | °C/W |

|                                 | θ <sub>JC</sub>    |                                                |             | 43                         |            |             | 43            |            | °C/W |

When disabled, the output assumes a high-impedance state.

See Typical Characteristic curves, Figure 39 through Figure 41.

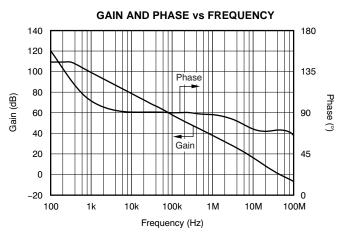

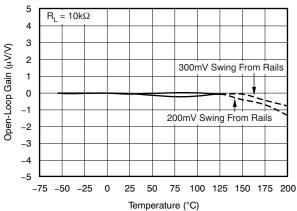

#### TYPICAL CHARACTERISTICS

At  $T_A = +25$ °C,  $V_S = \pm 18$ V, and  $R_L = 10$ k $\Omega$ , unless otherwise noted.

O.1Hz TO 10Hz NOISE

Time (1s/div)

Figure 5.

At  $T_A = +25$ °C,  $V_S = \pm 18$ V, and  $R_L = 10$ k $\Omega$ , unless otherwise noted.

**COMMON-MODE REJECTION RATIO** vs FREQUENCY 140 120 100 CMRR (dB) 80 60 40 20 0 10k 100k 10M 100M 1M

#### Figure 6.

Figure 7.

Frequency (Hz)

Figure 8.

Figure 9.

#### **OPEN-LOOP GAIN vs TEMPERATURE**

Figure 10.

At  $T_A$  = +25°C,  $V_S$  = ±18V, and  $R_L$  = 10k $\Omega$ , unless otherwise noted.

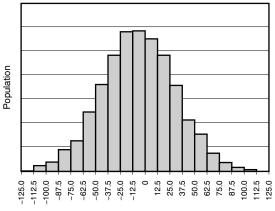

## OFFSET VOLTAGE PRODUCTION DISTRIBUTION

Offset Voltage ( $\mu V$ )

Figure 13.

Figure 15.

#### OFFSET VOLTAGE DRIFT PRODUCTION DISTRIBUTION

Figure 12.

#### OFFSET VOLTAGE vs COMMON-MODE VOLTAGE

Figure 14.

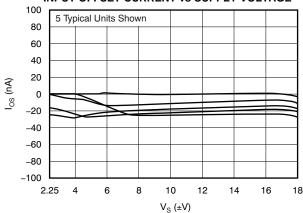

#### INPUT OFFSET CURRENT vs SUPPLY VOLTAGE

Figure 16.

At  $T_A = +25$ °C,  $V_S = \pm 18$ V, and  $R_L = 10$ k $\Omega$ , unless otherwise noted.

Figure 21.

Figure 22.

At  $T_A$  = +25°C,  $V_S$  = ±18V, and  $R_L$  = 10k $\Omega$ , unless otherwise noted.

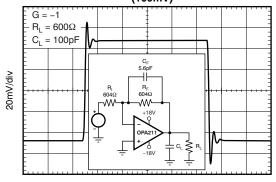

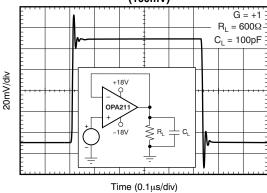

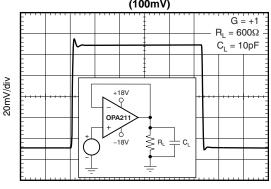

SMALL-SIGNAL STEP RESPONSE (100mV)

Time (0.1 μs/div) Figure 25.

SMALL-SIGNAL STEP RESPONSE (100mV)

Figure 27.

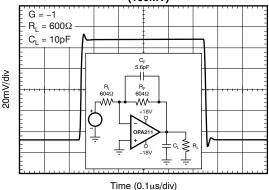

## SMALL-SIGNAL STEP RESPONSE (100mV)

Figure 24.

## SMALL-SIGNAL STEP RESPONSE (100mV)

Time (0.1 $\mu$ s/div)

Figure 26.

## SMALL-SIGNAL OVERSHOOT vs CAPACITIVE LOAD (100mV Output Step)

At  $T_A = +25$ °C,  $V_S = \pm 18$ V, and  $R_L = 10$ k $\Omega$ , unless otherwise noted.

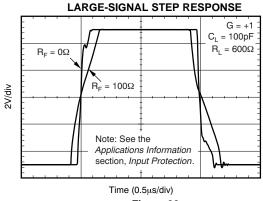

Figure 30.

Figure 31.

Figure 32.

Figure 33.

Figure 34.

At  $T_A$  = +25°C,  $V_S$  = ±18V, and  $R_L$  = 10k $\Omega$ , unless otherwise noted.

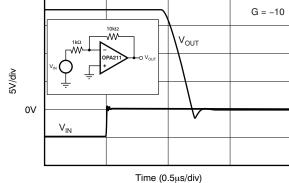

## **NEGATIVE OVERLOAD RECOVERY** G = -100V 5V/div $V_{\text{OUT}}$

Time (0.5µs/div) Figure 35.

**POSITIVE OVERLOAD RECOVERY**

Figure 36.

Figure 37.

Figure 38.

-5 -10 -15  $V_S = \pm 15V$ -20

Figure 40.

Submit Documentation Feedback

At  $T_A$  = +25°C,  $V_S$  = ±18V, and  $R_L$  = 10k $\Omega$ , unless otherwise noted.

#### APPLICATION INFORMATION

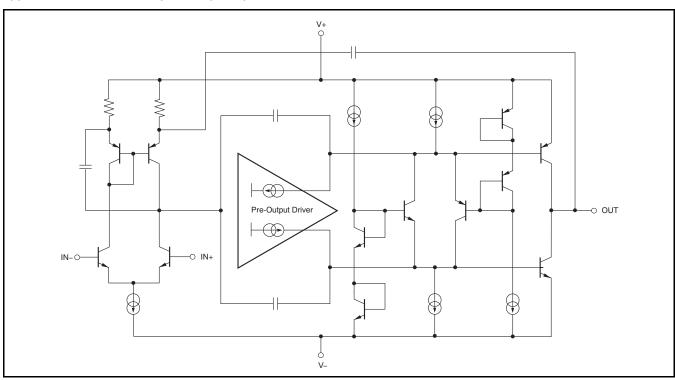

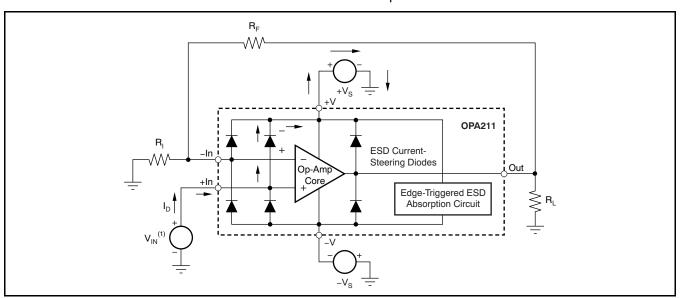

The OPA211 and OPA2211 are unity-gain stable, precision op amps with very low noise. Applications with noisy or high-impedance power supplies require decoupling capacitors close to the device pins. In most cases,  $0.1\mu F$  capacitors are adequate. Figure 42 shows a simplified schematic of the OPA211. This die uses a SiGe bipolar process and contains 180 transistors.

#### **OPERATING VOLTAGE**

OPA211 series op amps operate from ±2.25V to ±18V supplies while maintaining excellent performance. The OPA211 series can operate with as little as +4.5V between the supplies and with up to +36V between the supplies. However, some applications do not require equal positive and

negative output voltage swing. With the OPA211 series, power-supply voltages do not need to be equal. For example, the positive supply could be set to +25V with the negative supply at -5V or vice-versa.

The common-mode voltage must be maintained within the specified range. In addition, key parameters are assured over the specified temperature range,  $T_A = -40^{\circ}\text{C}$  to +125°C. Parameters that vary significantly with operating voltage or temperature are shown in the Typical Characteristics.

Figure 42. OPA211 Simplified Schematic

#### INPUT PROTECTION

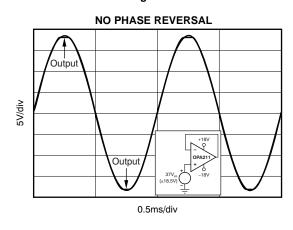

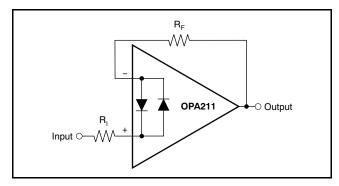

The input terminals of the OPA211 are protected from excessive differential voltage with back-to-back diodes, as shown in Figure 43. In most circuit applications, the input protection circuitry has no consequence. However, in low-gain or G = 1 circuits, fast ramping input signals can forward bias these diodes because the output of the amplifier cannot respond rapidly enough to the input ramp. This effect illustrated in Figure 30 of the Characteristics. If the input signal is fast enough to create this forward bias condition, the input signal current must be limited to 10mA or less. If the input signal current is not inherently limited, an input series resistor can be used to limit the signal input current. This input series resistor degrades the low-noise performance of the OPA211, and is discussed in the Noise Performance section of this data sheet. Figure 43 shows an example implementing a current-limiting feedback resistor.

Figure 43. Pulsed Operation

#### **NOISE PERFORMANCE**

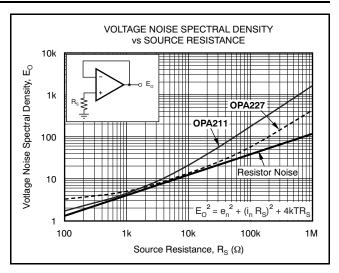

Figure 44 shows total circuit noise for varying source impedances with the op amp in a unity-gain configuration (no feedback resistor network, and therefore no additional noise contributions). Two different op amps are shown with total circuit noise calculated. The OPA211 has very low voltage noise, making it ideal for low source impedances (less than  $2k\Omega$ ). A similar precision op amp, the OPA227, has somewhat higher voltage noise but lower current noise. It provides excellent noise performance at moderate source impedance ( $10k\Omega$  to  $100k\Omega$ ). Above  $100k\Omega$ , a FET-input op amp such as the OPA132 (very low current noise) may provide improved performance. The equation in Figure 44 is shown for the calculation of the total circuit noise. Note that  $e_n =$ voltage noise,  $I_n$  = current noise,  $R_S$  = source impedance, k = Boltzmann's constant =  $1.38 \times 10^{-23}$ J/K, and T is temperature in K.

Figure 44. Noise Performance of the OPA211 and OPA227 in Unity-Gain Buffer Configuration

#### **BASIC NOISE CALCULATIONS**

Design of low-noise op amp circuits requires careful consideration of a variety of possible noise contributors: noise from the signal source, noise generated in the op amp, and noise from the feedback network resistors. The total noise of the circuit is the root-sum-square combination of all noise components.

The resistive portion of the source impedance produces thermal noise proportional to the square root of the resistance. This function is plotted in Figure 44. The source impedance is usually fixed; consequently, select the op amp and the feedback resistors to minimize the respective contributions to the total noise.

Figure 44 depicts total noise for varying source impedances with the op amp in a unity-gain configuration (no feedback resistor network, and therefore no additional noise contributions). The operational amplifier itself contributes both a voltage noise component and a current noise component. The voltage noise is commonly modeled as a time-varying component of the offset voltage. The current noise is modeled as the time-varying component of the input bias current and reacts with the source resistance to create a voltage component of noise. Therefore, the lowest noise op amp for a given application depends on the source impedance. For low source impedance, current noise is negligible and voltage noise generally dominates. For high source impedance, current noise may dominate.

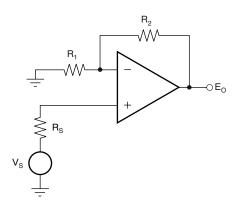

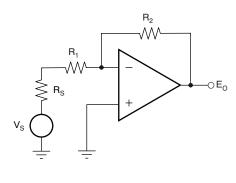

Figure 45 illustrates both inverting and noninverting op amp circuit configurations with gain. In circuit configurations with gain, the feedback network resistors also contribute noise. The current noise of the op amp reacts with the feedback resistors to create additional noise components. The feedback resistor values can generally be chosen to make these noise sources negligible. The equations for total noise are shown for both configurations.

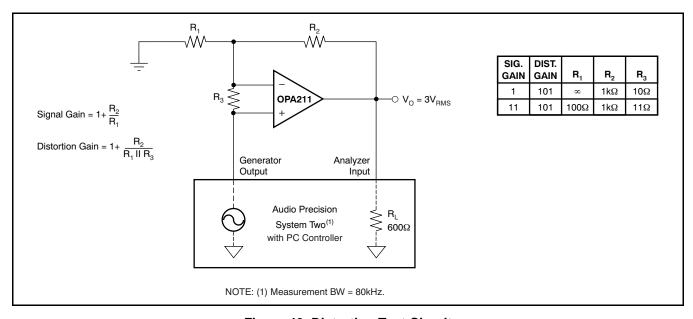

## TOTAL HARMONIC DISTORTION MEASUREMENTS

OPA211 series op amps have excellent distortion characteristics. THD + Noise is below 0.0001% (G = +1,  $V_O = 3V_{RMS}$ ) throughout the audio frequency range, 20Hz to 20kHz, with a 600 $\Omega$  load.

The distortion produced by OPA211 series op amps is below the measurement limit of many commercially available distortion analyzers. However, a special test circuit illustrated in Figure 46 can be used to extend the measurement capabilities.

Op amp distortion can be considered an internal error source that can be referred to the input. Figure 46 shows a circuit that causes the op amp distortion to be 101 times greater than that normally produced by the op amp. The addition of  $R_3$  to the otherwise standard noninverting amplifier configuration alters the feedback factor or noise gain of the circuit. The closed-loop gain is unchanged, but the feedback available for error correction is reduced by a factor of

101, thus extending the resolution by 101. Note that the input signal and load applied to the op amp are the same as with conventional feedback without  $R_3$ . The value of  $R_3$  should be kept small to minimize its effect on the distortion measurements.

Validity of this technique can be verified by duplicating measurements at high gain and/or high frequency where the distortion is within the measurement capability of the test equipment. Measurements for this data sheet were made with an Audio Precision System Two distortion/noise analyzer, which greatly simplifies such repetitive measurements. The measurement technique can, however, be performed with manual distortion measurement instruments.

#### SHUTDOWN

The shutdown (enable) function of the OPA211 is referenced to the positive supply voltage of the operational amplifier. A valid high disables the op amp. A valid high is defined as (V+) - 0.35V of the positive supply applied to the shutdown pin. A valid low is defined as (V+) - 3V below the positive supply pin. For example, with V<sub>CC</sub> at ±15V, the device is enabled at or below 12V. The device is disabled at or above 14.65V. If dual or split power supplies are used, care should be taken to ensure the valid high or valid low input signals are properly referred to the positive supply voltage. This pin must be connected to a valid high or low voltage or driven, and not left open-circuit. The enable and disable times are provided in the Typical Characteristics section (see Figure 39 through Figure 41). When disabled, the output assumes a high-impedance state.

#### Noise in Noninverting Gain Configuration

Noise at the output:

$$E_0^2 = \left[1 + \frac{R_2}{R_1}\right]^2 e_n^2 + e_1^2 + e_2^2 + (i_n^2 R_2)^2 + e_S^2 + (i_n^2 R_S)^2 \left[1 + \frac{R_2}{R_1}\right]^2$$

Where

$$e_S = \sqrt{4kTR_S} \times \left[1 + \frac{R_2}{R_1}\right]$$

= thermal noise of  $R_S$

$$e_1 = \sqrt{4kTR_1} \times \left(\frac{R_2}{R_1}\right) = \text{thermal noise of } R_1$$

$$e_2 = \sqrt{4kTR_2}$$

= thermal noise of  $R_2$

#### **Noise in Inverting Gain Configuration**

Noise at the output:

$$E_{O}^{2} = \left[1 + \frac{R_{2}}{R_{1} + R_{S}}\right]^{2} e_{n}^{2} + e_{1}^{2} + e_{2}^{2} + (i_{n}R_{2})^{2} + e_{S}^{2}$$

Where

$$e_S = \sqrt{4kTR_S} \times \left(\frac{R_2}{R_1 + R_S}\right)$$

= thermal noise of  $R_S$

$$e_1 = \sqrt{4kTR_1} \times \left[ \frac{R_2}{R_1 + R_S} \right]$$

= thermal noise of  $R_1$

$$e_2 = \sqrt{4kTR_2}$$

= thermal noise of  $R_2$

For the OPA211 series op amps at 1kHz,  $e_n = 1.1 \text{nV}/\sqrt{\text{Hz}}$  and  $i_n = 1.7 \text{pA}/\sqrt{\text{Hz}}$ .

Figure 45. Noise Calculation in Gain Configurations

Figure 46. Distortion Test Circuit

#### **ELECTRICAL OVERSTRESS**

Designers often ask questions about the capability of an operational amplifier to withstand electrical overstress. These questions tend to focus on the device inputs, but may involve the supply voltage pins or even the output pin. Each of these different pin functions have electrical stress limits determined by the voltage breakdown characteristics of the particular semiconductor fabrication process and specific circuits connected to the pin. Additionally, internal electrostatic discharge (ESD) protection is built into these circuits to protect them from accidental ESD events both before and during product assembly.

It is helpful to have a good understanding of this basic ESD circuitry and its relevance to an electrical overstress event. Figure 47 illustrates the ESD circuits contained in the OPA211 (indicated by the dashed line area). The ESD protection circuitry involves several current-steering diodes connected from the input and output pins and routed back to the internal power-supply lines, where they meet at an absorption device internal to the operational amplifier. This protection circuitry is intended to remain inactive during normal circuit operation.

An ESD event produces a short duration, high-voltage pulse that is transformed into a short duration, high-current pulse as it discharges through a semiconductor device. The ESD protection circuits are designed to provide a current path around the operational amplifier core to prevent it from being damaged. The energy absorbed by the protection circuitry is then dissipated as heat.

When an ESD voltage develops across two or more of the amplifier device pins, current flows through one or more of the steering diodes. Depending on the path that the current takes, the absorption device may activate. The absorption device has a trigger, or threshold voltage, that is above the normal operating voltage of the OPA211 but below the device breakdown voltage level. Once this threshold is exceeded, the absorption device quickly activates and clamps the voltage across the supply rails to a safe level.

When the operational amplifier connects into a circuit such as that illustrated in Figure 47, the ESD protection components are intended to remain inactive and not become involved in the application circuit operation. However, circumstances may arise where an applied voltage exceeds the operating voltage range of a given pin. Should this condition occur, there is a risk that some of the internal ESD protection circuits may be biased on, and conduct current. Any such current flow occurs through steering diode paths and rarely involves the absorption device.

(1)  $V_{IN} = +V_S + 500$ mV.

Figure 47. Equivalent Internal ESD Circuitry and Its Relation to a Typical Circuit Application

www.ti.com

Figure 47 depicts a specific example where the input voltage,  $V_{IN}$ , exceeds the positive supply voltage  $(+V_S)$  by 500mV or more. Much of what happens in the circuit depends on the supply characteristics. If  $+V_S$  can sink the current, one of the upper input steering diodes conducts and directs current to  $+V_S$ . Excessively high current levels can flow with increasingly higher  $V_{IN}$ . As a result, the datasheet specifications recommend that applications limit the input current to 10mA.

If the supply is not capable of sinking the current,  $V_{IN}$  may begin sourcing current to the operational amplifier, and then take over as the source of positive supply voltage. The danger in this case is that the voltage can rise to levels that exceed the operational amplifier absolute maximum ratings. In extreme but rare cases, the absorption device triggers on while  $+V_{S}$  and  $-V_{S}$  are applied. If this event happens, a direct current path is established between the  $+V_{S}$  and  $-V_{S}$  supplies. The power dissipation of the absorption device is quickly exceeded, and the extreme internal heating destroys the operational amplifier.

Another common question involves what happens to the amplifier if an input signal is applied to the input while the power supplies  $+V_S$  and/or  $-V_S$  are at 0V. Again, it depends on the supply characteristic while at 0V, or at a level below the input signal amplitude. If the supplies appear as high impedance, then the operational amplifier supply current may be supplied by the input source via the current steering diodes. This state is not a normal bias condition; the amplifier most likely will not operate normally. If the supplies are low impedance, then the current through the steering diodes can become quite high. The current level depends on the ability of the input source to deliver current, and any resistance in the input path.

#### **DFN PACKAGE**

The OPA211 is offered in an DFN-8 package (also known as SON). The DFN package is a QFN package with lead contacts on only two sides of the bottom of the package. This leadless package maximizes board space and enhances thermal and electrical characteristics through an exposed pad.

DFN packages are physically small, and have a smaller routing area, improved thermal performance, and improved electrical parasitics. Additionally, the absence of external leads eliminates bent-lead issues.

The DFN package can be easily mounted using standard printed circuit board (PCB) assembly techniques. See Application Note *QFN/SON PCB Attachment* (SLUA271) and Application Report *Quad Flatpack No-Lead Logic Packages* (SCBA017), both available for download at www.ti.com.

The exposed leadframe die pad on the bottom of the package must be connected to V-. Soldering the thermal pad improves heat dissipation and enables specified device performance.

#### **DFN LAYOUT GUIDELINES**

The exposed leadframe die pad on the DFN package should be soldered to a thermal pad on the PCB. A mechanical drawing showing an example layout is attached at the end of this data sheet. Refinements to this layout may be necessary based on assembly process requirements. Mechanical drawings located at the end of this data sheet list the physical dimensions for the package and pad. The five holes in the landing pattern are optional, and are intended for use with thermal vias that connect the leadframe die pad to the heatsink area on the PCB.

Soldering the exposed pad significantly improves board-level reliability during temperature cycling, key push, package shear, and similar board-level tests. Even with applications that have low-power dissipation, the exposed pad must be soldered to the PCB to provide structural integrity and long-term reliability.

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type    | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|--------------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| OPA211AID        | ACTIVE                | SOIC               | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| OPA211AIDG4      | ACTIVE                | SOIC               | D                  | 8    | 75             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| OPA211AIDGKR     | ACTIVE                | MSOP               | DGK                | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| OPA211AIDGKRG4   | ACTIVE                | MSOP               | DGK                | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| OPA211AIDGKT     | ACTIVE                | MSOP               | DGK                | 8    | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| OPA211AIDGKTG4   | ACTIVE                | MSOP               | DGK                | 8    | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| OPA211AIDR       | ACTIVE                | SOIC               | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| OPA211AIDRG4     | ACTIVE                | SOIC               | D                  | 8    | 2500           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| OPA211AIDRGR     | ACTIVE                | SON                | DRG                | 8    | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| OPA211AIDRGRG4   | ACTIVE                | SON                | DRG                | 8    | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| OPA211AIDRGT     | ACTIVE                | SON                | DRG                | 8    | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| OPA211AIDRGTG4   | ACTIVE                | SON                | DRG                | 8    | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| OPA211ID         | PREVIEW               | SOIC               | D                  | 8    |                | TBD                       | Call TI          | Call TI                      |

| OPA211IDGKR      | PREVIEW               | MSOP               | DGK                | 8    |                | TBD                       | Call TI          | Call TI                      |

| OPA211IDGKT      | PREVIEW               | MSOP               | DGK                | 8    |                | TBD                       | Call TI          | Call TI                      |

| OPA211IDR        | PREVIEW               | SOIC               | D                  | 8    |                | TBD                       | Call TI          | Call TI                      |

| OPA211IDRGR      | PREVIEW               | SON                | DRG                | 8    |                | TBD                       | Call TI          | Call TI                      |

| OPA211IDRGT      | PREVIEW               | SON                | DRG                | 8    |                | TBD                       | Call TI          | Call TI                      |

| OPA2211AIDDA     | PREVIEW               | SO<br>Power<br>PAD | DDA                | 8    | 75             | TBD                       | Call TI          | Call TI                      |

| OPA2211AIDDAR    | PREVIEW               | SO<br>Power<br>PAD | DDA                | 8    | 2500           | TBD                       | Call TI          | Call TI                      |

| OPA2211AIDRGR    | PREVIEW               | SON                | DRG                | 8    | 1000           | TBD                       | Call TI          | Call TI                      |

| OPA2211AIDRGT    | PREVIEW               | SON                | DRG                | 8    | 250            | TBD                       | Call TI          | Call TI                      |

<sup>&</sup>lt;sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. **TBD:** The Pb-Free/Green conversion plan has not been defined.

#### PACKAGE OPTION ADDENDUM

6-Nov-2008

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

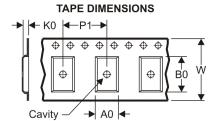

#### TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       |      | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------|--------------------|---|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| OPA211AIDGKR | MSOP | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3     | 3.4     | 1.4     | 8.0        | 12.0      | Q1               |

| OPA211AIDGKT | MSOP | DGK                | 8 | 250  | 180.0                    | 12.4                     | 5.3     | 3.4     | 1.4     | 8.0        | 12.0      | Q1               |

| OPA211AIDR   | SOIC | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4     | 5.2     | 2.1     | 8.0        | 12.0      | Q1               |

| OPA211AIDRGR | SON  | DRG                | 8 | 1000 | 330.0                    | 12.4                     | 3.3     | 3.3     | 1.1     | 8.0        | 12.0      | Q2               |

| OPA211AIDRGT | SON  | DRG                | 8 | 250  | 180.0                    | 12.4                     | 3.3     | 3.3     | 1.1     | 8.0        | 12.0      | Q2               |

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA211AIDGKR | MSOP         | DGK             | 8    | 2500 | 346.0       | 346.0      | 29.0        |

| OPA211AIDGKT | MSOP         | DGK             | 8    | 250  | 190.5       | 212.7      | 31.8        |

| OPA211AIDR   | SOIC         | D               | 8    | 2500 | 346.0       | 346.0      | 29.0        |

| OPA211AIDRGR | SON          | DRG             | 8    | 1000 | 346.0       | 346.0      | 29.0        |

| OPA211AIDRGT | SON          | DRG             | 8    | 250  | 190.5       | 212.7      | 31.8        |

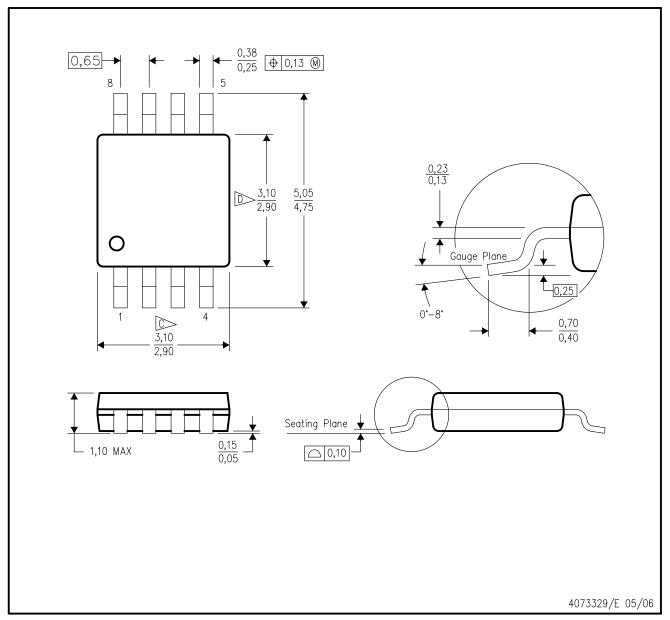

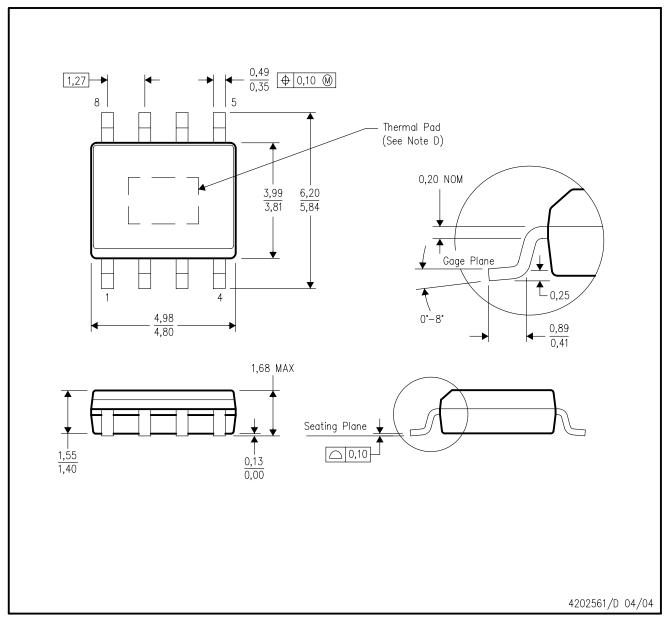

## DGK (S-PDSO-G8)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

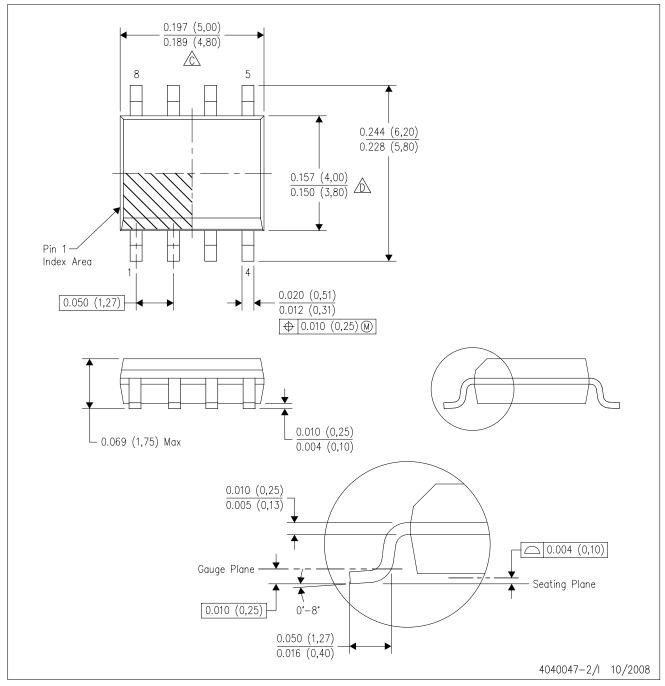

## D (R-PDSO-G8)

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 (0,15) per end.

- Body width does not include interlead flash. Interlead flash shall not exceed .017 (0,43) per side.

- E. Reference JEDEC MS-012 variation AA.

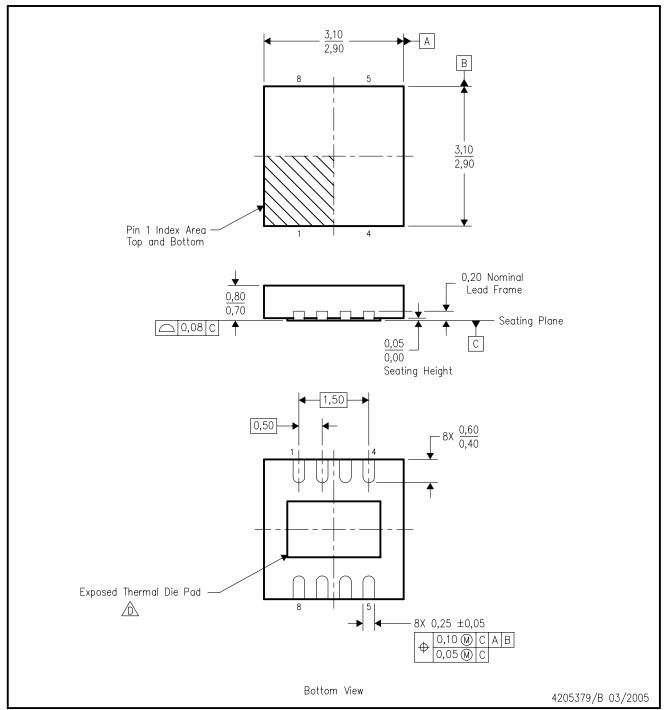

## DRG (S-PDSO-N8)

### PLASTIC SMALL OUTLINE

- All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994. NOTES:

- B. This drawing is subject to change without notice.C. SON (Small Outline No-Lead) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

- E. JEDEC MO-229 package registration pending.

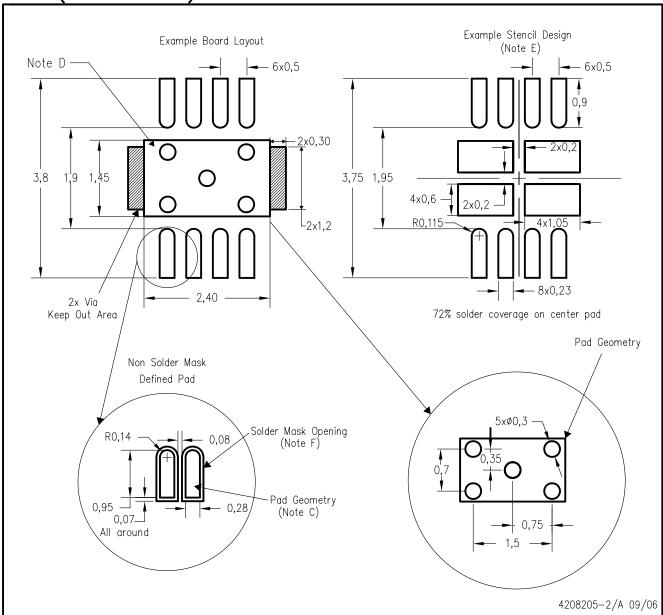

## THERMAL PAD MECHANICAL DATA DRG (S-PDSO-N8)

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, Quad Flatpack No-Lead Logic Packages, Texas Instruments Literature No. SCBA017. This document is available at www.ti.com.

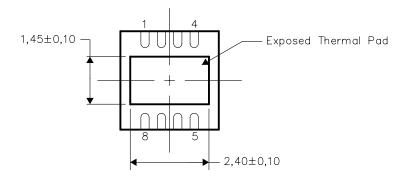

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

## DRG (S-PDSO-N8)

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-SM-782 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SCBA017, SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="https://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

## DDA (R-PDSO-G8)

## PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="https://www.ti.com">www.ti.com</a>.

PowerPAD is a trademark of Texas Instruments.

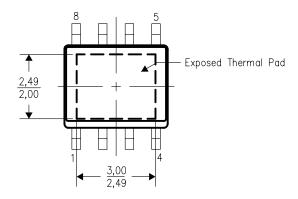

## THERMAL PAD MECHANICAL DATA DDA (R-PDSO-G8)

#### THERMAL INFORMATION

This PowerPAD  $^{\text{TM}}$  package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated